US009023688B1

# (12) United States Patent Or-Bach et al.

# (54) METHOD OF PROCESSING A SEMICONDUCTOR DEVICE

(71) Applicant: Monolithic 3D Inc., San Jose, CA (US)

(72) Inventors: **Zvi Or-Bach**, San Jose, CA (US); **Brian Cronquist**, San Jose, CA (US); **Albert Karl Henning**, Palo Alto, CA (US)

(73) Assignee: Monolithic 3D Inc., San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/298,917

(22) Filed: Jun. 7, 2014

#### Related U.S. Application Data

- (60) Provisional application No. 61/889,500, filed on Oct. 10, 2013, provisional application No. 61/832,922, filed on Jun. 9, 2013.

- (51) Int. Cl.

H01L 21/00 (2006.01)

H01L 21/8238 (2006.01)

H01L 21/20 (2006.01)

H01L 21/44 (2006.01)

H01L 21/768 (2006.01)

### (10) Patent No.:

US 9,023,688 B1

(45) **Date of Patent:**

May 5, 2015

### (52) U.S. Cl.

CPC ...... *H01L 21/76885* (2013.01)

####

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 2002/0175401 | A1* | 11/2002 | Huang et al | 257/686 |

|--------------|-----|---------|-------------|---------|

| 2004/0156172 | A1* | 8/2004  | Lin et al   | 361/704 |

| 2008/0142937 | A1* | 6/2008  | Chen et al  | 257/675 |

<sup>\*</sup> cited by examiner

Primary Examiner — Mohsen Ahmadi

#### (57) ABSTRACT

A method for processing a semiconductor device, the method including; providing a first semiconductor layer including first transistors; forming interconnection layers overlying the transistors, where the interconnection layers include copper or aluminum; forming a shielding heat conducting layer overlaying the interconnection layers; forming an isolation layer overlaying the shielding heat conducting layer; forming a second semiconductor layer overlying the isolation layer, and processing the second semiconductor layer at a temperature greater than about  $400^{\circ}$  C., where the interconnection layers are kept at a temperature below about  $400^{\circ}$  C.

#### 20 Claims, 22 Drawing Sheets

## METHOD OF PROCESSING A SEMICONDUCTOR DEVICE

This application claims benefit of provisional U.S. Patent Application No. 61/889,500, filed on Oct. 10, 2013, and provisional U.S. Patent Application No. 61/832,922, filed on Jun. 9, 2013. This application claims priority to the foregoing applications. The contents of the foregoing applications are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This application relates to the general field of Integrated Circuit (IC) devices and fabrication methods, and more particularly to multilayer or Three Dimensional Integrated Circuit (3D-IC) devices and fabrication methods.

#### 2. Discussion of Background Art

Over the past 40 years, there has been a dramatic increase in functionality and performance of Integrated Circuits (ICs). 20 This has largely been due to the phenomenon of "scaling"; i.e., component sizes within ICs have been reduced ("scaled") with every successive generation of technology. There are two main classes of components in Complementary Metal Oxide Semiconductor (CMOS) ICs, namely transistors and wires. With "scaling", transistor performance and density typically improve and this has contributed to the previouslymentioned increases in IC performance and functionality. However, wires (interconnects) that connect together transistors degrade in performance with "scaling". The situation 30 today is that wires dominate the performance, functionality and power consumption of ICs.

3D stacking of semiconductor devices or chips is one avenue to tackle the wire issues. By arranging transistors in 3 dimensions instead of 2 dimensions (as was the case in the 35 1990s), the transistors in ICs can be placed closer to each other. This reduces wire lengths and provides low wiring delay and interconnect energy costs.

There are many techniques to construct 3D stacked integrated circuits or chips including:

Through-silicon via (TSV) technology: Multiple layers of transistors (with or without wiring levels) can be constructed separately. Following this, they can be bonded to each other and connected to each other with through-silicon vias (TSVs).

Monolithic 3D technology: With this approach, multiple layers of transistors and wires can be monolithically constructed. Some monolithic 3D approaches are described in U.S. Pat. Nos. 8,273,610, 8,557,632, 8,581, 349, 8,163,581, 8,378,715, 8,379,458, 8,742,476, 8,642, 50 416, 8,687,399, US patent publications 2013/0083589 and 2013/0241026, and pending U.S. patent application Ser. Nos. 13/274,161, 13/803,437, 13/836,080 and 13/796,930. The contents of the foregoing patents, publications, and applications are incorporated herein by 55 reference.

An early work on monolithic 3D was presented in U.S. Pat. No. 7,052,941 and follow-on work in related patents includes U.S. Pat. No. 7,470,598. A technique which has been used over the last 20 years to build SOI wafers, called "Smart-Cut" 60 or "Ion-Cut", was presented in U.S. Pat. No. 7,470,598 as one of the options to perform layer transfer for the formation of a monolithic 3D device. Yet in a related patent disclosure, by the same inventor of U.S. Pat. No. 7,470,598, U.S. application Ser. No. 12/618,542 it states: "In one embodiment of the 65 previous art, exfoliating implant method in which ion-implanting Hydrogen into the wafer surface is known. But this

2

exfoliating implant method can destroy lattice structure of the doped layer 400 by heavy ion-implanting. In this case, to recover the destroyed lattice structure, a long time thermal treatment in very high temperature is required. This long time/high temperature thermal treatment can severely deform the cell devices of the lower region." Moreover, in U.S. application Ser. No. 12/635,496 by the same inventor is stated: [0034] Among the technologies to form the detaching layer, one of the well known technologies is Hydrogen Exfoliating Implant. This method has a critical disadvantage which can destroy lattice structures of the substrate because it uses high amount of ion implantation. In order to recover the destroyed lattice structures, the substrate should be cured by heat treatment in very high temperature long time. This kind of high temperature heat treatment can damage cell devices in the lower regions." Furthermore, in U.S. application Ser. No. 13/175,652 it is stated: "Among the technologies to form the detaching layer 207, one technology is called as exfoliating implant in which gas phase ions such as hydrogen is implanted to form the detaching layer, but in this technology, the crystal lattice structure of the multiple doped layers 201, 203, 205 can be damaged. In order to recover the crystal lattice damage, a thermal treatment under very high temperature and long time should be performed, and this can strongly damage the cell devices underneath." In fact the Inventor had posted a video infomercial on his corporate website, and was up-loaded on YouTube on Jun. 1, 2011, clearly stating in reference to the Smart Cut process: "The wafer bonding and detaching method is well-known SOI or Semiconductor-On-Insulator technology. Compared to conventional bulk semiconductor substrates, SOI has been introduced to increase transistor performance. However, it is not designed for 3D IC either. Let me explain the reasons . . . . The dose of hydrogen is too high and, therefore, semiconductor crystalline lattices are demolished by the hydrogen ion bombardment during the hydrogen ion implantation. Therefore, typically annealing at more than 1,100 Celsius is required for curing the lattice damage after wafer detaching. Such high temperature processing certainly destroys underlying devices and intercon-40 nect layers. Without high temperature annealing, the transferred layer should be the same as a highly defective amorphous layer. It seems that there is no way to cure the lattice damage at low temperatures. BeSang has disruptive 3D layer formation technology and it enables formation of defect-free single crystalline semiconductor layer at low temperatures . . . '

In at least one embodiment presented herein, at least one innovative method and device structure to repair the crystal lattice damage caused by the hydrogen implant is described.

Regardless of the technique used to construct 3D stacked integrated circuits or chips, heat removal is a serious issue for this technology. For example, when a layer of circuits with power density P is stacked atop another layer with power density P, the net generated power density is 2P. Removing the heat produced due to this power density is a significant challenge. In addition, many heat producing regions in 3D stacked integrated circuits or chips have a high thermal resistance to the heat sink, and this makes heat removal even more difficult

Several solutions have been proposed to tackle this issue of heat removal in 3D stacked integrated circuits and chips. These are described in the following paragraphs.

Publications have suggested passing liquid coolant through multiple device layers of a 3D-IC to remove heat. This is described in "Microchannel Cooled 3D Integrated Systems", Proc. Intl. Interconnect Technology Conference, 2008 by D. C. Sekar, et al., "Forced Convective Interlayer

Cooling in Vertically Integrated Packages," Proc. Intersoc. Conference on Thermal Management (ITHERM), 2008 by T. Brunschweiler, et al., and "High Performance Heat Sinking for VLSI," IEEE Electron Device Letters, vol. EDL-2, No. 5, May 1981, by D. B. Tuckerman and R. F. W. Pease.

Thermal vias have been suggested as techniques to transfer heat from stacked device layers to the heat sink. Use of power and ground vias for thermal conduction in 3D-ICs has also been suggested. These techniques are described in "Allocating Power Ground Vias in 3D ICs for Simultaneous Power 10 and Thermal Integrity" ACM Transactions on Design Automation of Electronic Systems (TODAES), May 2009 by Hao Yu, Joanna Ho and Lei He.

In addition, thermal limitations during IC fabrication have been a big obstacle on the road to monolithic three-dimen- 15 sional ICs. The semiconductor and microelectronic processing techniques to form transistors, circuits, and devices, such as, for example, to form some silicon oxides or nitrides, repair damages from processes such as etching and ion-implantation, annealing and activation of ion implanted species, and 20 epitaxial regrow techniques, have processing temperatures (for example, greater than 400° C.) and times at temperature that would damage and harm the underlying metallization and/or device layers and structures. These processes may involve transient (short timescales, such as less than 500 ns 25 short or long wavelength laser pulses) heat exposures to the wafer/substrate being processed, or steady state applications (such as RTA, RTO, spike, flash, CVD, ALD, furnace/oven) of heat and/or heated material, substrates, susceptors or gases that may have processing times of seconds, minutes, or hours. 30

The passage of thermal energy through an insulating material may occur through three mechanisms; solid conductivity, gaseous conductivity, and radiative (infrared) transmission. The sum of these three components gives the total thermal conductivity of the material. Solid conductivity is an intrinsic 35 property of a specific material. For dense silica, solid conductivity is relatively high (a single-pane window transmits a large amount of thermal energy). However, a substance such as, for example, silica aerogels possess a very small (~1-10%) fraction of solid silica. Additionally, the solids that are present 40 consist of very small particles linked in a three-dimensional network (with many "dead-ends"). Therefore, thermal transport through the solid portion of silica aerogel occurs through a very tortuous path and is not particularly effective. The space not occupied by solids in an aerogel is normally filled 45 with air (or another gas) unless the material is sealed under vacuum. These gases can also transport thermal energy through the aerogel. The pores of silica aerogel are open and allow the passage of gas (albeit with difficulty) through the material. The final mode of thermal transport through silica 50 aerogels involves infrared radiation. Silica aerogels are also reasonably transparent in the infrared (especially for wavelengths between 3 and 5 microns), whereas carbon aerogels are not. At low temperatures, the radiative component of thermal transport is low, and not a significant problem. At 55 higher temperatures, radiative transport becomes the dominant mode of thermal conduction, and must be dealt with by, for example, incorporation of IR absorbing materials (opacification) in the aerogel matrix, such as carbon black or TiO<sub>2</sub>. The heat transport may then become by conductive means. 60 Other materials, for example, nanostructured oxides and metals, utilized phonon scattering and reflection mechanisms to provide a thermal barrier.

Aerogels are low-density solid-state materials derived from gel in which the liquid component of the gel has been 65 replaced with gas. Aerogels consist of a complicated crosslinked internal structure of chains of the aerogel constituent 4

molecules with a large number of air/gas/vacuum filled pores that take up most of the volume. Aerogels are commonly synthesized by the Sol-gel process, yet there are many variations of the process. Details are in the referenced documents and in the general industry knowledge base. In general, the Sol-gel process could be described as formation of an oxide network through polycondensation reactions of a molecular precursor in a liquid. The formation of aerogels usually involves two major steps, the formation of a wet gel, and the drying of the wet gel to form an aerogel. Silica aerogels may be prepared from silicon alkoxide precursors. The most common of these are tetramethyl orthosilicate (TMOS, Si (OCH<sub>3</sub>)<sub>4</sub>), and tetraethyl orthosilicate (TEOS, (OCH<sub>2</sub>CH<sub>3</sub>)<sub>4</sub>). However, many other alkoxides, containing various organic functional groups, can be used to impart different properties to the gel. The initial step in the formation of aerogels is hydrolysis and condensation of alkoxide. As condensation reactions progress the sol will set into a rigid gel. The kinetics of the reaction can be impracticably slow at room temperature, often requiring several days to reach completion. For this reason, acid or base catalysts are added to the formulation. These catalysts speed up the hydrolysis of silicon alkoxide. In acidic environments the oxygen atom in Si—OH or Si—OR is protonated and H—OH or HOR are good leaving groups. The electron density is shifted from the Si atom, making it more accessible for reaction with water. In basic environments nucleophilic attack by OH— occurs on the central Si atom. The amount and type of catalyst used play key roles in the microstructural, physical and optical properties of the final aerogel product. For example aerogels prepared with acid catalysts often show more shrinkage during supercritical drying and are less transparent than base catalyzed aerogels. As reaction progresses, the sol reaches the gel point, that is, the point in time at which the network of linked oxide particles spans the container holding the Sol. At the gel point the Sol becomes an Alcogel. Typical acid or base catalyzed TEOS gels are often classified as "single-step" gels, referring to the "one-pot" nature of this reaction. A more recently developed approach uses pre-polymerized TEOS as the silica source. Pre-polymerized TEOS is prepared by heating an ethanol solution of TEOS with a sub-stoichiometric amount of water and an acid catalyst. This material is redissolved in ethanol and reacted with additional water under basic conditions until gelation occurs. Gels prepared in this way are known as "two-step" acid-base catalyzed gels. These slightly different processing conditions impart subtle, but important changes to the final aerogel product. Single-step base catalyzed aerogels are typically mechanically stronger, but more brittle, than two-step aerogels. While two-step aerogels have a smaller and narrower pore size distribution and are often optically clearer than single-step aerogels. A most important step in the process in making silica aerogels is supercritical drying. This is where the liquid within the gel is removed, leaving only the linked silica network. The process can be performed by venting the ethanol above its critical point (high temperature-very dangerous) or by prior solvent exchange with CO<sub>2</sub> followed by supercritical venting (lower temperatures-less dangerous). The alcogels are placed in the autoclave (which has been filled with ethanol). The system is pressurized to at least 750-850 psi with CO2 and cooled to 5-10 degrees C. Liquid  $CO_2$  is then flushed through the vessel until all the ethanol has been removed from the vessel and from within the gels. When the gels are ethanol-free the vessel is heated to a temperature above the critical temperature of CO<sub>2</sub> (31 degrees C.). As the vessel is heated the pressure of the system rises. CO2 is carefully released to maintain a pressure slightly above the critical pressure of CO<sub>2</sub> (1050

psi). The system is held at these conditions for a short time, followed by the slow, controlled release of  $\mathrm{CO}_2$  to ambient pressure. Under these conditions, the network structure is retained and a gel with large pores is formed. The density of the resulting aerogel will be very low generally somewhere around 0.1 g/cm³. If the gel is dried by evaporation, then the capillary forces will result in shrinkage, the gel network will collapse, and a xerogel is formed.

The methods of preparing silica aerogels are not very successful in the case of carbon aerogels mainly due to the effects 10 of steric hindrance in tetra alkyl ethers. Instead a variant of the Sol-gel process is used. The precursor that is generally used in the synthesis of carbon aerogels is a resorcinol-formaldehyde solution. Polycondensation of resorcinol with formaldehyde in aqueous solutions leads to gels that can be super critically dried with CO2 to form organic aerogels which are called resorcinolformaldehyde (RF) aerogels. Carbon aerogels can be obtained by pyrolysis of resorcinol formaldehyde aerogels in an inert atmosphere. Additives can be included to the base aerogel formulation to reduce the IR radiative properties; 20 these additives can be carbon black, TiO<sub>2</sub> and others. (NASA Tech Briefs, November 2009, Nesmith et al.) Many aero & xerogel matrices are damaged during processing such as plasma etching and depositing layers over the matrix. Often it is found that using a post processing treatment will help to 25 heal the damage or at least mitigate the changes that occurred during processing. These post treatments can also be used to make the films hydrophobic. Many papers discuss these treatments for porous Methylsilsesquioxane (MSQ) and aerogel films. (Fruehauf, S., et al., "Hydrophobisation process for 30 porous Low K Dielectric Silica Layers," Advanced Metallization Conference, Materials Research Society, 287-294 (2010); Gurav, J. L., et al., "Silica Aerogel: Synthesis and Applications," Journal of Nanomaterials, vol. 2010, id. 409310)

Techniques to remove heat from 3D Integrated Circuits and Chips and protect sensitive metallization and circuit elements from either the heat of processing of the 3D layers or the operationally generated heat from an active circuit, will be beneficial.

Additionally the 3D technology according to some embodiments of the invention may enable some very innovative IC alternatives with reduced development costs, increased yield, and other illustrative benefits.

#### **SUMMARY**

The invention may be directed to multilayer or Three Dimensional Integrated Circuit (3D IC) devices, fabrication methods, and processing equipment.

In one aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection 65 layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shield-

6

ing heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises heating said second semiconductor layer to greater than about 800° C. for more than a minute to form an oxide.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises heating said second semiconductor layer to greater than about 800° C. to repair etch damage of said second semiconductor layer.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer to greater than about 825° C. to form a Bottom Interface Layer.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises a rapid thermal anneal for greater than about 20 seconds at greater than about 700° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said sec-

ond semiconductor layer comprises a chemical vapor deposition of amorphous silicon at greater than about 600° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises heating said second semiconductor layer to greater than about 800° C. to form a dummy gate oxide.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises a rapid thermal anneal for greater than about 5 seconds in the presence of nitrogen at greater than about 700° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection 35 layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises performing selective epitaxy of SiGe or SiC at greater than about 600° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises a rapid thermal anneal at greater than 440° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding

8

heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises a thermal anneal at greater than about 500° C. to perform an ion-cut cleave.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said second semiconductor layer comprises a thermal anneal greater than about 500° C. to anneal H+ implant damage.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said shielding layer is kept at a temperature below about 400° C., wherein said keeping said interconnection layers are at a temperature below about 400° C. comprises cooling a vacuum chuck holding said device and having a plurality of thermal vias connecting said first semiconductor layer to said shielding heat conducting layer.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said device comprises dicing streets and wherein said keeping said shielding layer at a temperature below 400° C. comprises having a plurality of thermal vias disposed within said dicing streets to remove heat from said shielding heat conducting layer.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said sec-

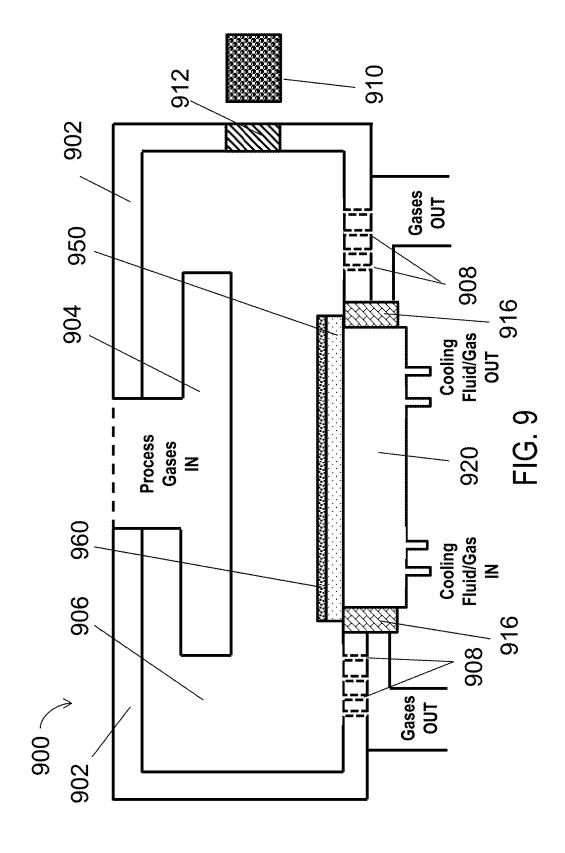

ond semiconductor layer comprises use of processing equipment comprising a chuck to hold said device, wherein said chuck is actively cooled.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconduc- 5 tor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said processing said sec- 15 ond semiconductor layer comprises use of processing equipment comprising a chuck to hold said device and a processing chamber, said processing chamber comprises a thermal isolation structure to isolate said chuck from said processing chamber.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor tor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said transistors are kept at a temperature below about 400° C.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said shielding heat conducting layer is constructed to provide at least 2 times higher heat conduction in the horizontal direction than in the vertical 60 direction.

In another aspect, a method for processing a semiconductor device, the method comprising; providing a first semiconductor layer comprising first transistors; forming interconnection layers overlying said transistors, wherein said interconnection layers comprise copper or aluminum; forming a shielding heat conducting layer overlaying said interconnection

10

layers; forming an isolation layer overlaying said shielding heat conducting layer; forming a second semiconductor layer overlying said isolation layer, and processing said second semiconductor layer at a temperature greater than about 400° C., wherein said interconnection layers are kept at a temperature below about 400° C., wherein said shielding heat conducting layer comprises tungsten.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Various embodiments of the invention will be understood and appreciated more fully from the following detailed description, taken in conjunction with the drawings in which:

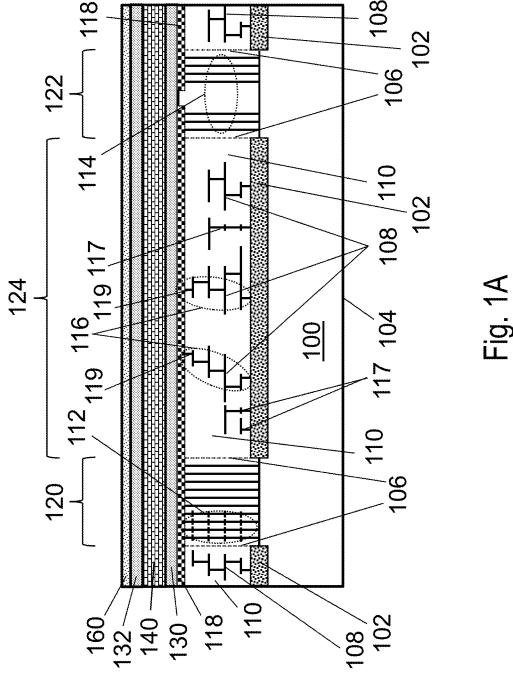

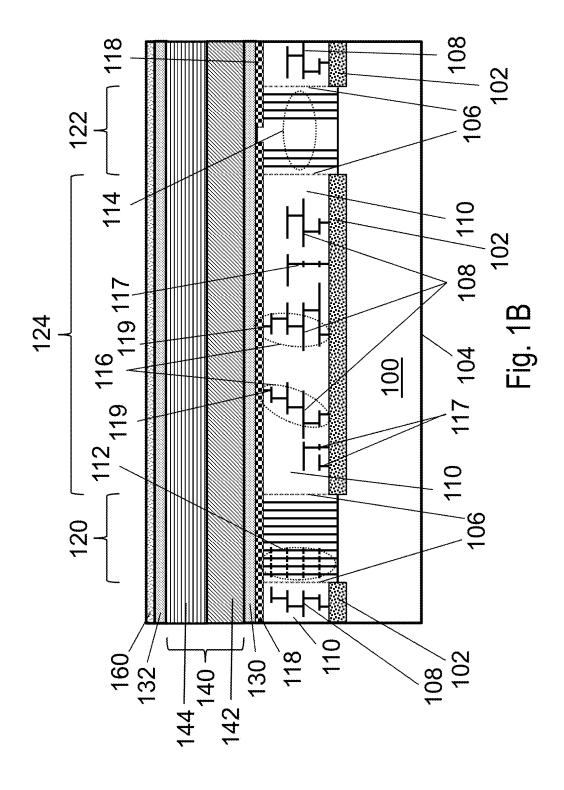

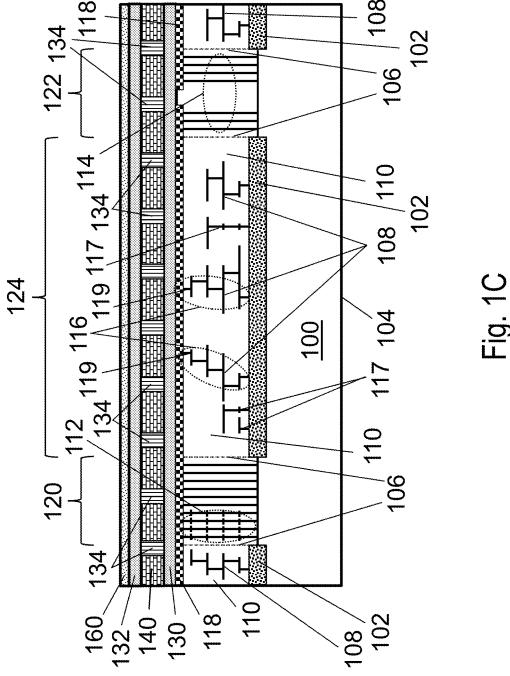

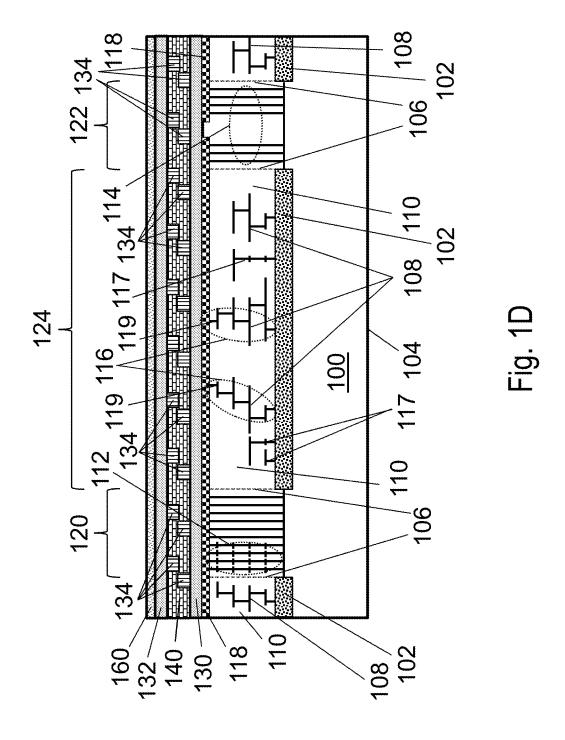

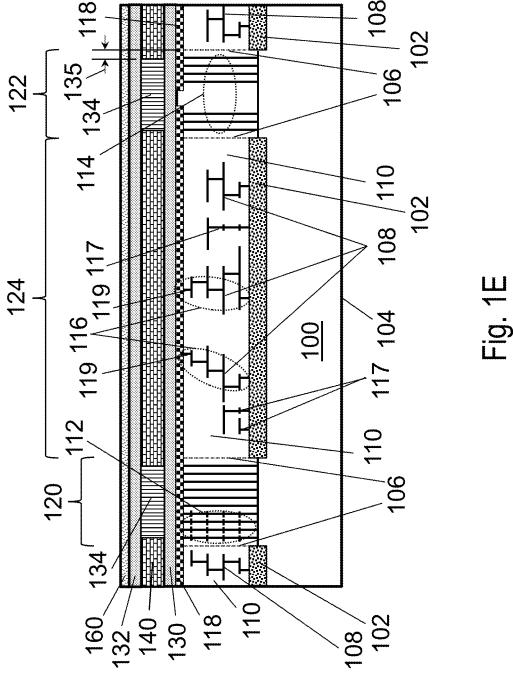

FIGS. 1A-1E are exemplary drawing illustrations of protective structures to protect the desired regions of substrate devices from high processing and operating temperatures;

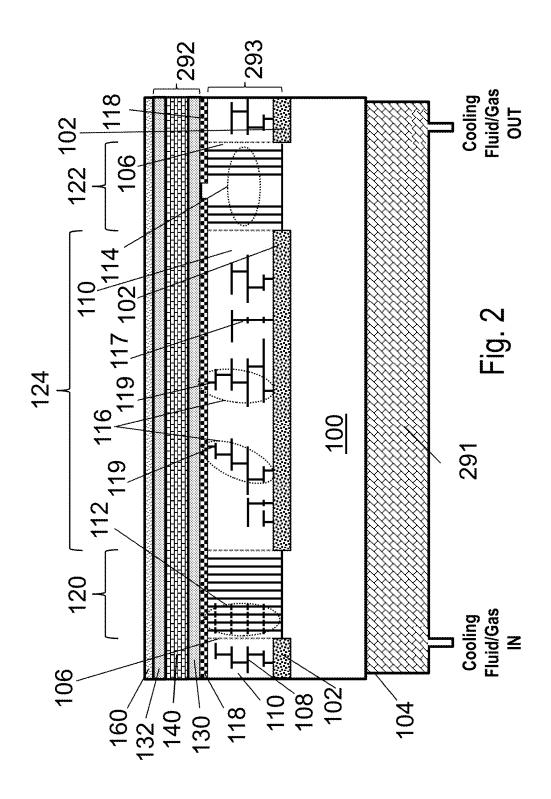

FIG. 2 is an exemplary drawing illustration of protective structures and a cooling device to model thermal conduction of the structures;

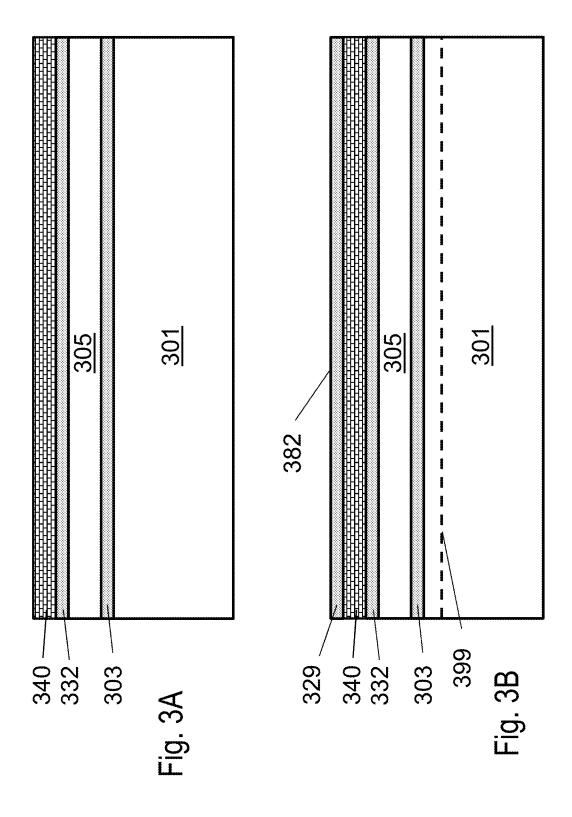

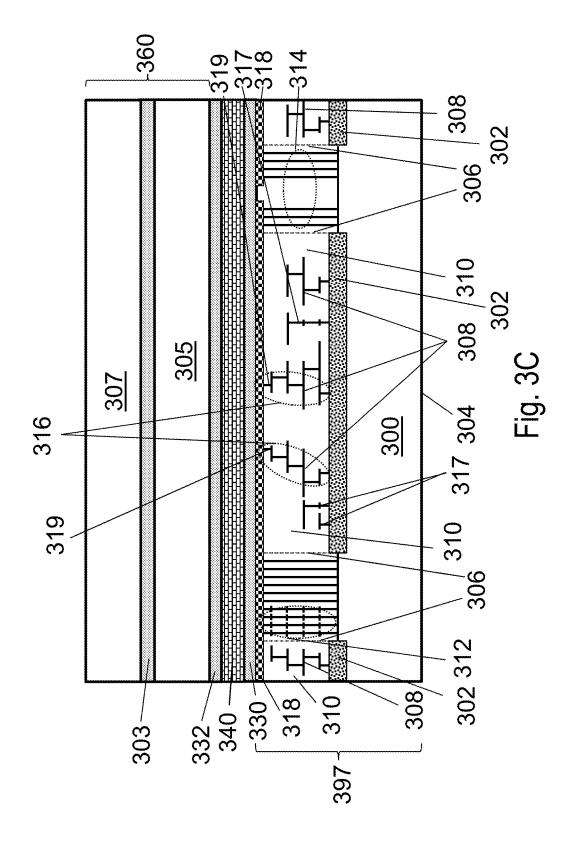

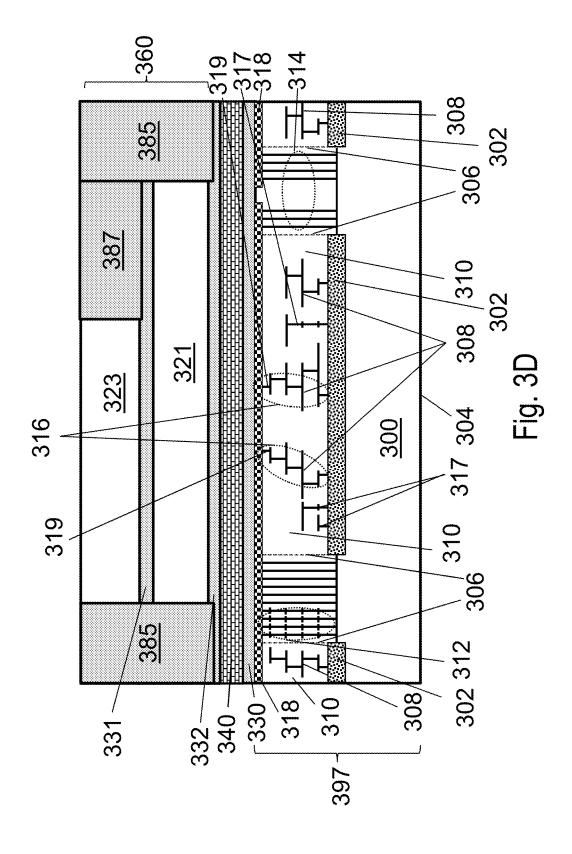

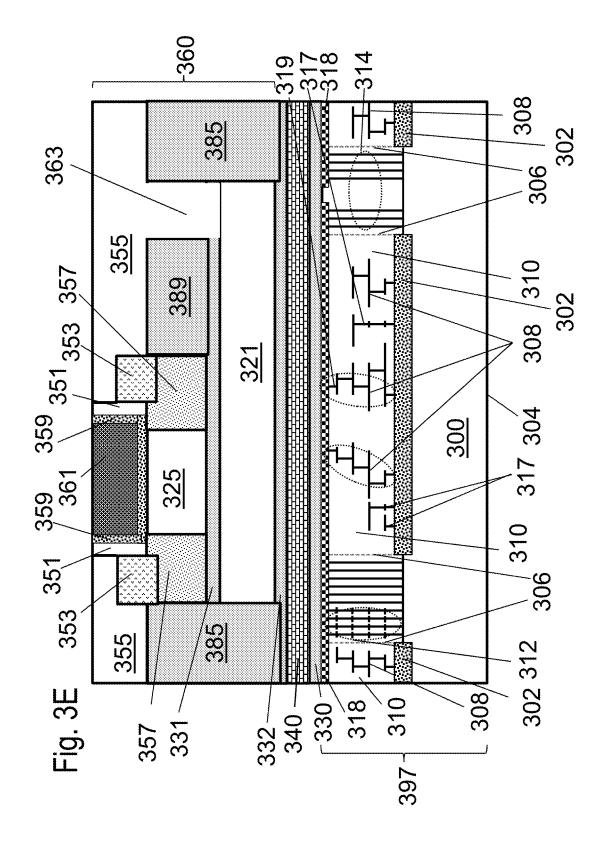

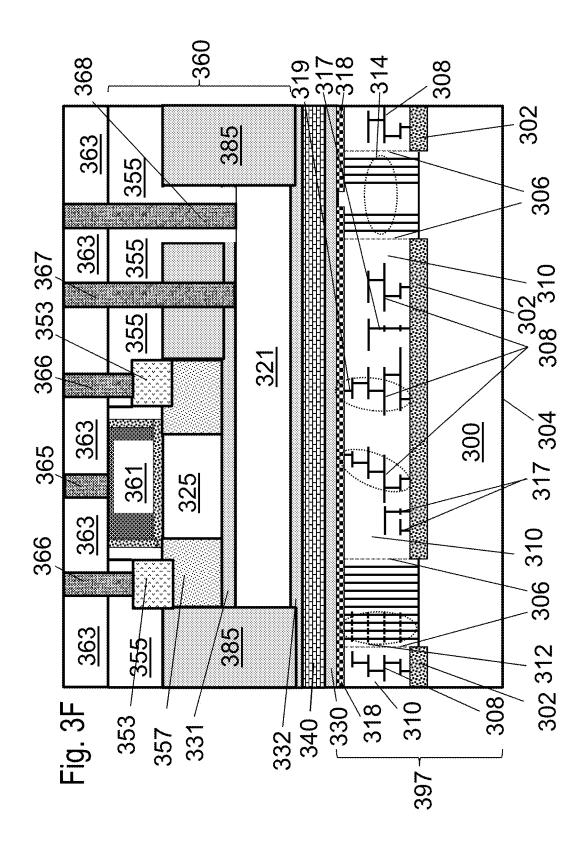

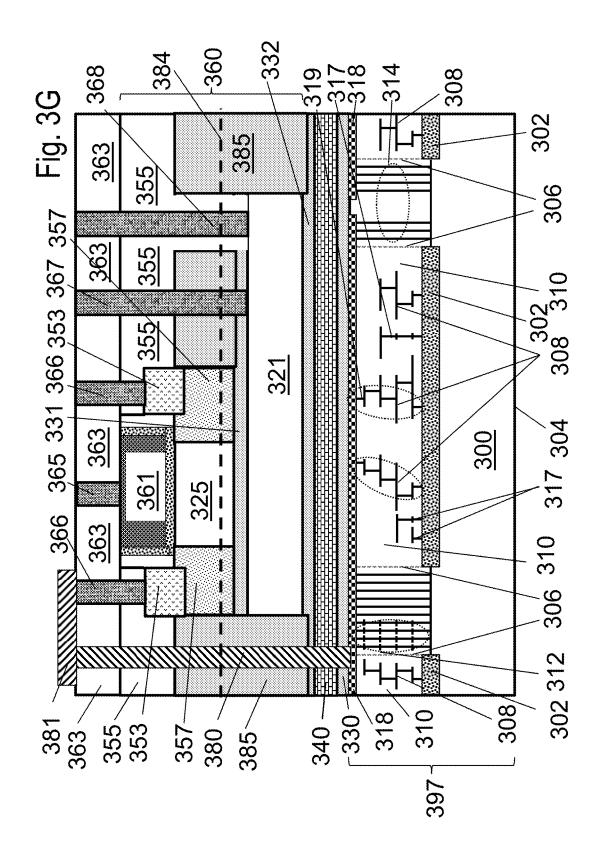

FIGS. **3A-3**G are exemplary drawing illustrations of a process to form an exemplary re-channel FD-MOSFET with integrated Thermal Protection Structures and Thermal Isolation layer;

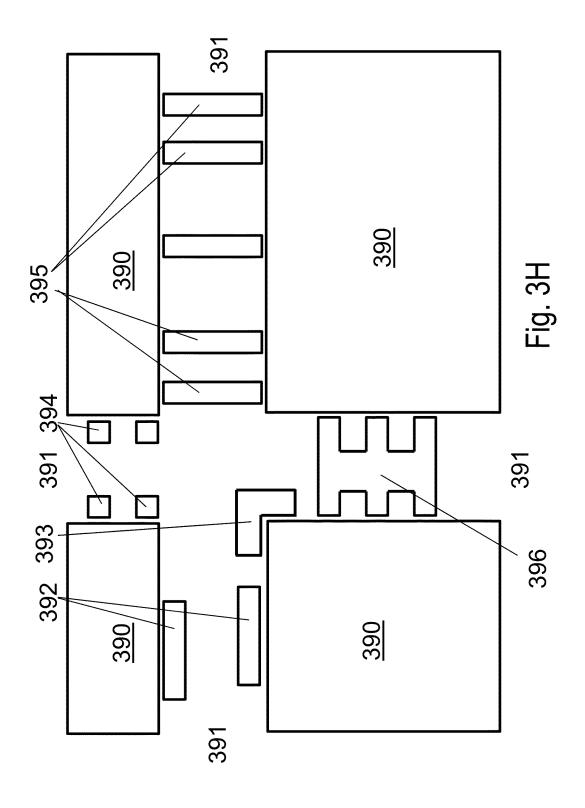

FIG. 3H is an exemplary drawing illustration of guidepost structures:

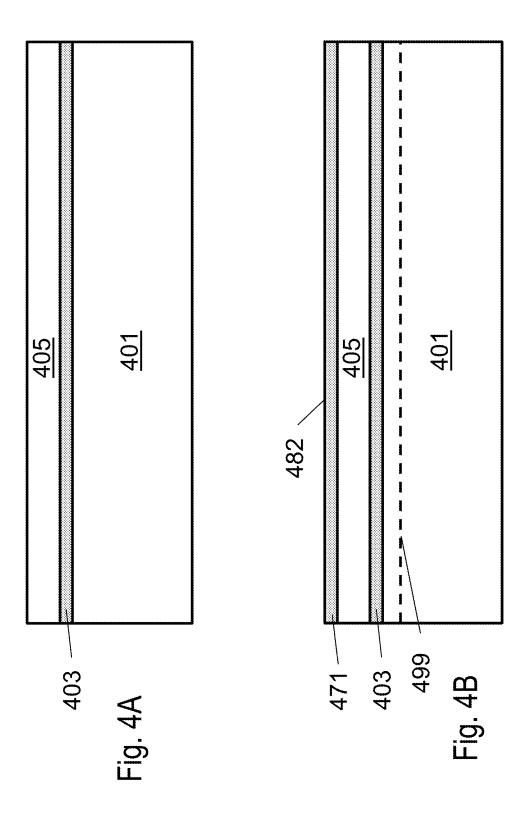

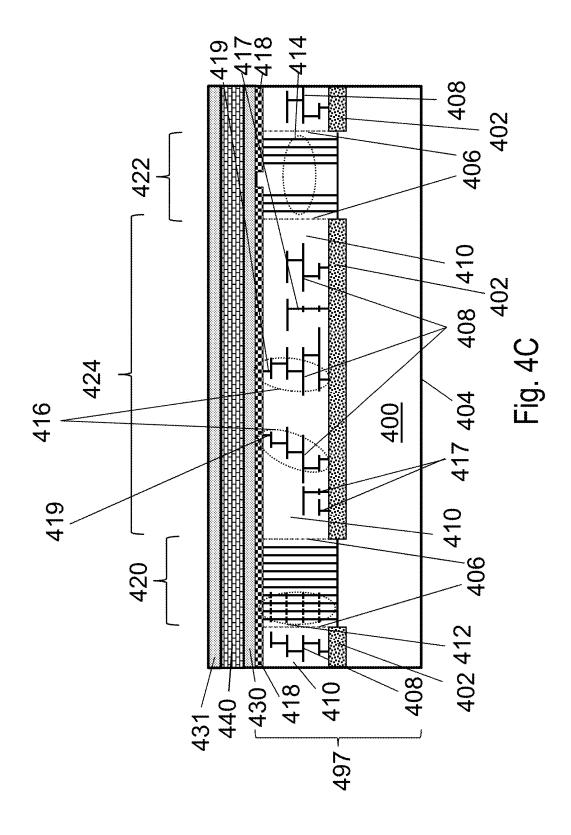

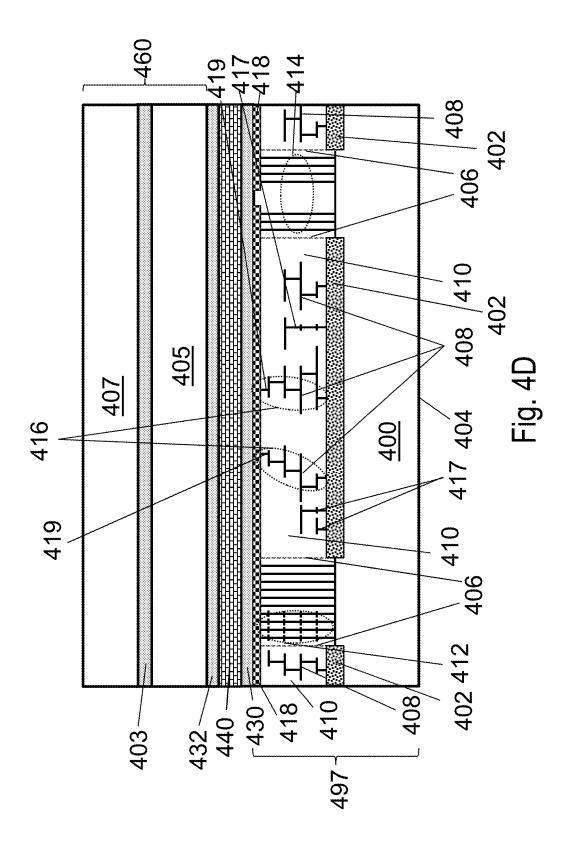

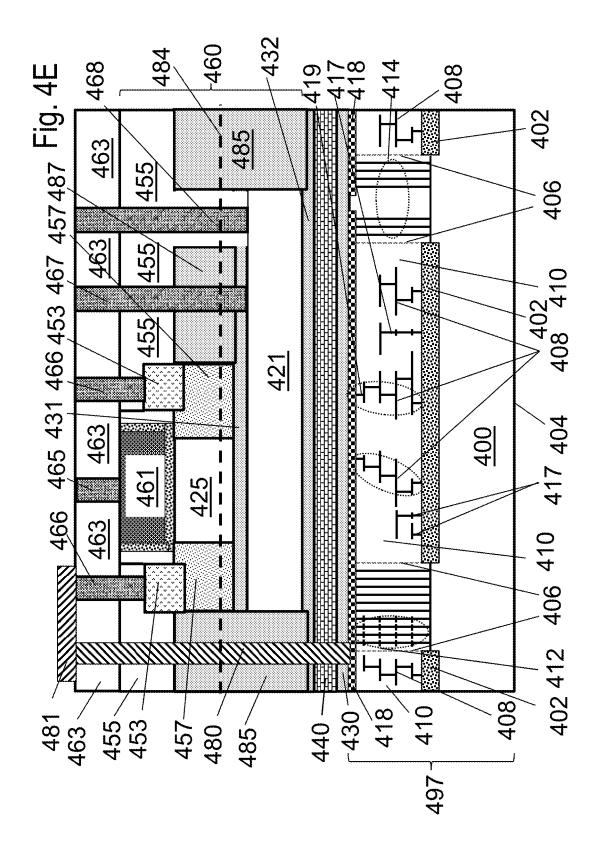

FIGS. **4**A-**4**E are exemplary drawing illustrations of another process to form an exemplary n-channel FD-MOS-FET with integrated Thermal Protection Structures and Thermal Isolation layer;

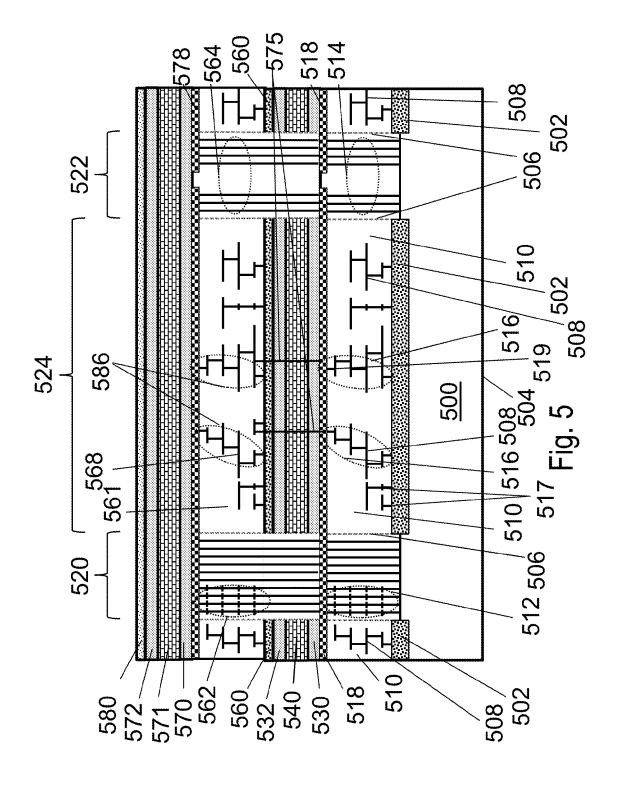

FIG. 5 is an exemplary drawing illustration of a multi-strata device with protective structures to protect the desired regions of strata and substrate devices from high processing and operating temperatures;

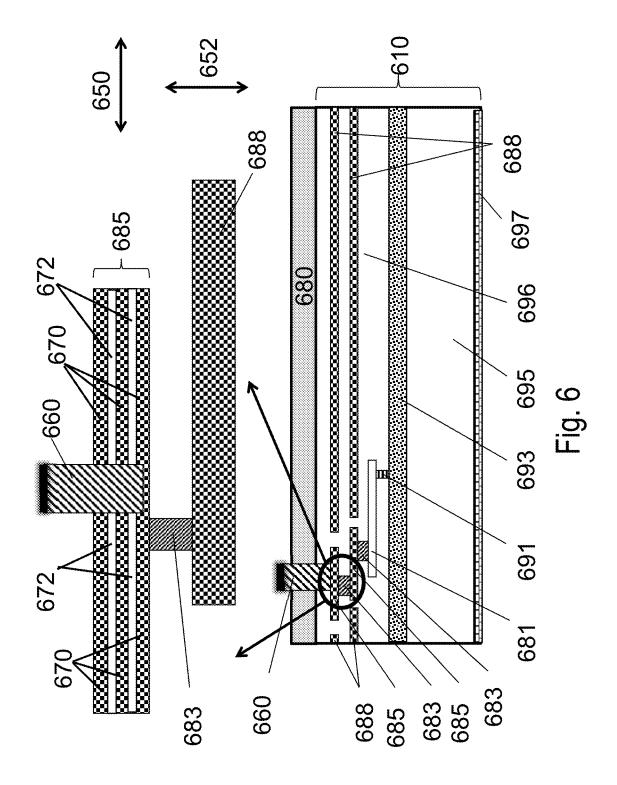

FIG.  $\mathbf{6}$  is an exemplary drawing illustration of a layered shield layer or region;

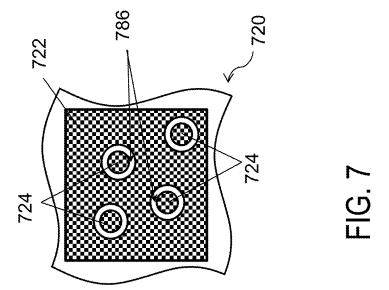

FIG. 7 is an exemplary drawing illustration of a shield layer or layers or regions that may have isolated TLV landing pads;

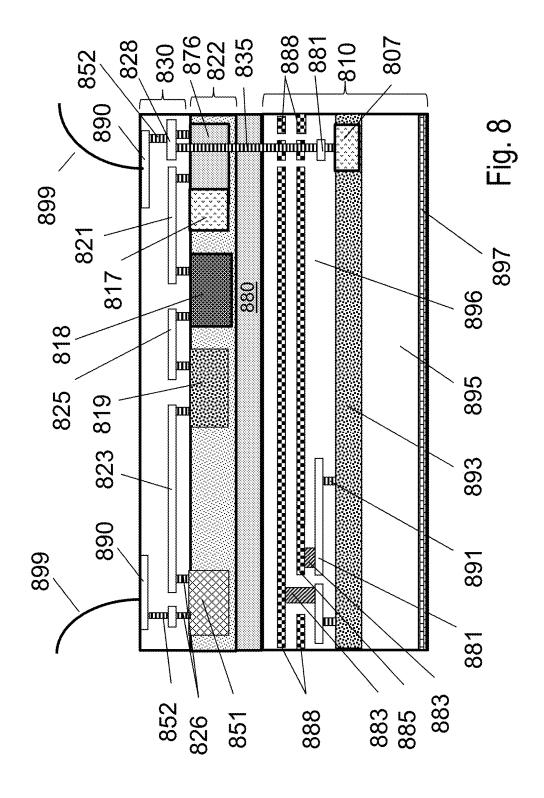

FIG. **8** is an exemplary illustration of some additional embodiments and combinations of devices, circuits, paths, and connections of a 3D device; and

FIG. 9 is an exemplary drawing illustration of a portion of thermally enhanced processing equipment.

#### DETAILED DESCRIPTION

An embodiment of the invention is now described with reference to the drawing figures. Persons of ordinary skill in the art will appreciate that the description and figures illustrate rather than limit the invention and that in general the figures are not drawn to scale for clarity of presentation. Such skilled persons will also realize that many more embodiments are possible by applying the inventive principles contained herein and that such embodiments fall within the scope of the invention which is not to be limited except by the appended claims.

Some drawing figures may describe process flows for building devices. The process flows, which may be a sequence of steps for building a device, may have many structures, numerals and labels that may be common between two or more adjacent steps. In such cases, some labels, numerals and structures used for a certain step's figure may have been described in the previous steps' figures.

A portion of the steps in a semiconductor process flow, for example, a high speed CMOS FinFet or UTBB-FDSOI (Ultra Thin Body and BOX—Fully Depleted Silicon On Insulator) transistor flow, may have processing temperatures which would damage the metallization (for example, copper or alu-

minum) and isolation layers (for example, low-k dielectrics, thermally conductive aerogels) in the substrate interconnect layers or regions, or change the device electrical characteristics and reliability of devices (for example, transistors, capacitors, inductors, resistors) that reside in or on the sub- 5 strate. For example, processes such as Si<sub>3</sub>N<sub>4</sub> LPCVD depositions for STI and well formations (typically about 30 minutes at 700° C.), STI liner oxidation (typically about 10 minutes at 800-1000° C.), STI TEOS/Flowable CVD densification (typically about 20 minutes at 1000° C.), well implant 10 activation (typically about 10 seconds at 1000° C.), dummy gate oxide (typically minutes at 800° C.), dummy gate amorphous silicon (a-Si) deposition (typically about 20 minutes at 600° C.), SiGe and SiC selective epi (typically 10s of minutes at 600-700° C.), silicide formation (typically minutes of RTA at 400-500° C.), S/D, halo, Vt implant anneals (typically spike of seconds at 950° C. plus a flash or laser 3 ms exposure at 1350° C.); BIL bottom interface layer (ox+Nstuffing) (typically minutes at 825  $^{\circ}$  C.),  $HfO_{2}$  post-ALD N anneal (typically about 30 seconds at 700° C.).

An embodiment of the invention is a structure that will thermally protect the metallization, isolation layers, device electrical characteristics and reliability of devices that may reside in or on the substrate, or which may reside in or on a previously constructed layer/stratum in the 3D stack, from 25 damaging processes and processing temperatures, for example, such damaging processes and processing temperatures as described above. This thermal protective structure (TPS) may be effectively increasing the average thermal conductivity of the device layer it is protecting as well as itself. 30 This protective structure may be utilized in combination or sub-combination with a thermal isolation layer (TIL), thermally enhanced substrate (TES) and modified processing equipment that is described elsewhere in this document and in other related applications.

As illustrated in FIG. 1A, TPS protective structures to protect the desired regions of substrate devices may be constructed. These protective structures may be constructed using conventional and known processing techniques. A substrate 100, for example, a monocrystalline silicon wafer which may be thermally enhanced (a Thermally Enhanced Substrate—TES—as described elsewhere herein), of which a portion is shown in FIG. 1, may have substrate device regions 102 including devices, such as, for example, transistors, capacitors, and resistors. These substrate device regions 102 could be formed as eventual product dice with surrounding scribelanes and die edge seals. The devices within the regions of substrate devices could be wholly or partially within the substrate 100 material. The scribelanes may also be called dicing streets or scribelines.

The substrate 100 may also have a backside surface 104 that may be utilized to conduct processing heat (the heat source may be the layer being processed 160 during device formation steps or portions of the equipment performing the processing such as IR lamps and chamber walls) from the 55 substrate 100 to a processing equipment cooling chuck or other thermal conduction/heat removal device, generally within the processing equipment.

The substrate device regions 102 may have corresponding regions of substrate metallization 108 and BEOL isolation 60 110 interconnect layers, which may include copper or aluminum metallization materials and low-k dielectric inter-metal dielectrics (IMD) respectively.

As part of the construction of or separately from the formation of regions of substrate metallization 108 and BEOL 65 isolation 110 interconnect layers, one or more shield layer or regions 118 of metallization and isolation may be con-

12

structed. Details are in referenced applications. For example, the shield layer or regions 118 metallization may include materials such as tungsten, copper, aluminum, graphene, and DLC, materials with a high thermal conductivity and an appropriate melting/softening point. The shield layer or regions 118 may be constructed as a continuous slab across substantially the entire extant of the substrate area, or may be formed as regions.

The shield layer or regions 118 may have terminations within the device die scribelanes. The shield layer or regions 118 may include TLV (Thru Layer Via) landing pads wherein signals from the second layer of devices may connect either to a lower shield layer (for example shield layer or regions 118) or to the interconnect layers or regions of substrate metallization 108 and BEOL isolation 110 interconnect or lower layer devices, transistors and circuits. The shield layer or regions 118 may be thermally but not electrically connected or may be thermally and electrically connected to the substrate 100 in a variety of ways as described herein and in referenced incorporated documents.

The scribelanes, for example, scribelane with thermal via stacks and continuous shield 120 and/or scribelane with thermal via stacks and cut shield layer 122, may be substantially populated with thermal via stacks, which may be formed as thermal via stacks with via landing pads 112 as each metallization and via layer of the regions of substrate metallization 108 and BEOL isolation 110 interconnect layers are formed, or the thermal vias in the scribelane 114 may be formed as an etched and filled deep-via prior to the formation of the shield layer or regions 118. Forming the thermal via stack after the regions of substrate metallization 108 and BEOL isolation 110 interconnect layers are formed may provide the use of a different BEOL isolation material, material that may be more thermally isolative and/or thermally stable, for the thermal via stacks than for the devices. The thermal vias in the scribelane 114 may also be formed as one or a few to substantially fill (with appropriate stress relief structures) the scribelane with metal (thermally conductive) material (as much as practical given CMP dishing design rules) that may be part of the shield layer formation, or may be formed in a separate metal deposition and planarization step and may provide use of a more thermally conductive material than copper or aluminum to form the thermal vias in the scribelane 114, for example, carbon nanotubes, Plasma Enhanced Chemical Vapor Deposited Diamond Like Carbon-PECVD DLC (about 1000 W/m-K), and Chemical Vapor Deposited (CVD) graphene (about 5000 W/m-K). Refractory metals may be employed as a shield material as well, for example, Tungsten.

As dictated by design choices, the thermal vias (such as, for example, substantially all or a portion of thermal via stacks with via landing pads 112 and/or thermal vias in the scribelane 114, and/or in-die thermal via stacks 116 and/or fill-in thermal paths 117) may truncate in a dielectrically isolated or reverse biased junction electrically isolated connection to the substrate, or the thermal vias may truncate as a conventional forward biased junction or no junction substrate contact that may be thermally and electrical connected to the substrate. Processing, structure, and operational details are in referenced applications.

In-die thermal via stacks 116 (may also be called in-die thermal via paths) may also be constructed over the regions of substrate devices 102 (within die extant 124) by forming a via stack that utilizes the interconnect structures of the regions of substrate metallization 108 and BEOL isolation 110 interconnect layers, with a via connection 119 from the shield layer to a metallization layer/segment within the regions of substrate metallization 108 and BEOL isolation 110 interconnect lay-

ers. Via connection 119 may be connected at a later step to electrically couple to the second layer devices (such as a TLV), or may primarily enable (as part of a thermal path) a thermal connection from substrate 100 to shield layer or regions 118. Details of this formation have been described in 5 referenced applications.

Additionally, as a matter of design choice and may be controlled by an EDA design and placement algorithm, fill-in thermal paths 117 may be added to a chip die design/layout to maximize local and die average thermal conductivity. The 10 fill-in thermal paths 117 may be formed anywhere on the die and from any level of the regions of substrate metallization 108 and BEOL isolation 110 interconnect layers to the substrate 100, for example, metal 1 to substrate, metal 3 to substrate, and so on). Fill-in thermal paths 117 may be added 15 to a power or ground line as extra thermal connections to the substrate 100, which may be electrically conductive or nonconductive due to design constraints. Fill-in thermal paths 117 may be additional connections beyond what a conventional design or EDA tool may provide/construct. Fill-in ther- 20 mal paths 117 may be added to/formed in so called 'white space' within the device die, where there may be a path vertically and horizontally thru the regions of substrate metallization 108 and BEOL isolation 110 interconnect layers to the substrate 100. Moreover, fill-in thermal paths 117 may be 25 formed from the CMP fill structures of one or more of the regions of substrate metallization 108 and BEOL isolation 110 interconnect layers.

As a matter of design choice, die seal 106 (or die seal-ring) may be utilized as a thermal connection from either interconnect metal layers of the ring itself or the shield layer or regions 118 to the substrate 100.

Lower isolation layer 130 may be deposited on top of shield layer or regions 118 to protect and electrically and partially thermally isolate above and below and may include 35 the bonding oxides for an ion-cut layer transfer process (for example, the case wherein TIL 140 is formed on a donor wafer or substrate). Lower isolation layer 130 may include designed-in voids (not shown), for example, by etch removal of portions of lower isolation layer 130, thus forming regions 40 of vacuum and/or gas and regions of the remaining material (for example, silicon oxide) of lower isolation layer 130. The voids may be formed such that they extend fully or partially thru the entire thickness lower isolation layer 130. The presence of the voids may reduce the average thermal conductiv- 45 ity of lower isolation layer 130. The voids may include greater than about 5%, greater than about 10%, greater than about 20%, or greater than about 50% of the area and/or volume of lower isolation layer 130, thus affecting the total average lower isolation layer 130 thermal conductivity by greater than 50 about 5%, or greater than about 50%.

TIL 140 may be formed of materials and structures to thermally isolate the layers below it (for example, substrate metallization 108 and BEOL isolation 110 interconnect layers, substrate device regions 102, shield layer or regions 118) 55 from a portion of the processing heat of the layers above (such as layer being processed 160). TIL 140 may include materials and construction that provide at least about a 10 times, or 20 times, or 50 times, or 100 times lower thermal conductivity than layer being processed 160, and/or upper isolation layer 60 132, and/or lower isolation layer 130, and/or regions of substrate metallization 108 and BEOL isolation 110, and/or substrate 100. TIL 140 may have an effective thermal conductivity of less than about 20 mW/m-K, less than about 50 mW/m-K, less than about 100 mW/m-K, less than about 200 mW/m- 65 K, less than about 500 mW/m-K. TIL 140 may have a thickness of less than about 10 nm, less than about 20 nm, less

14

than about 50 nm, less than about 100 nm, less than about 200 nm, less than about 500 nm, less than about 1 um, less than about 2 um, less than about 10 um, less than about 20 um. The design choices of TIL 140 material thermal conductivity and thickness may be guided by desired effective size and/or density of TLVs achievable, maximum temperature of layer being processed 160 during device construction and processing, time at temperature and/or temperature profile of layer being processed 160 during device construction and processing, number of stack layers, mechanical strength, the cooling capacity of the cooled chuck and/or TES (microchannel for example), and so on. For example, a very low thermal conductivity material of about 100 mW/m-K (at the processing temperature of interest) may enable a minimum TIL 140 thickness of less than about 800 nm for a maximum temperature of layer being processed 160 of about 1000° C. or a minimum TIL 140 thickness of less than about 550 nm for a maximum temperature of layer being processed 160 of about 800° C., given no equipment cooling capacity constraints.

TIL 140 may include aerogels, well-known for providing low thermal conductivities. For example, thin film silica aerogels, such as the Aerogel B-Pyrolyzed material measured in M. L. Bauer, et al., "Thin-film aerogel thermal conductivity measurements via  $3\omega$ ", Journal of Non-Crystalline Solids, 357 (2011) 2960-2965 [Bauer] incorporated herein by reference, provide a thermal conductivity of 24 mW/m-K at a thickness of 370 nm, deposited on and capped by SiO<sub>2</sub>. IR (Infra-Red) transmittance may be suppressed by adding IR absorbing or scattering materials (opacification) in the aerogel matrix, such as, for example, carbon black or TiO<sub>2</sub>. For example, in J. Wang, et al., "Monolithic silica aerogel insulation doped with TiO<sub>2</sub> powder and ceramic fibers", Journal of Non-Crystalline Solids, 186 (1995) 296-300 [JWang] incorporated herein by reference, a thermal conductivity of 38 mW/m-K at 800° K in air was obtained. Chemical vapor infiltration may be utilized to opacify the aerogel. The opacification agent may be added during the sol-gel process or after the supercritical drying step. The opacification agent may also increase thermal stability and allow use of the aerogel at higher temperatures. The top portion of the aerogel may be opacified to absorb the IR component of the upper layer heating and the lower portion of the aerogel that is not opacified can thermally isolate the vibrational component of the heat. The aerogel may be strengthened when placed under compressive stress, which may be accomplished by tuning the stress of the deposited capping layer. The gaseous component of the thermal conduction may be minimized by placing the aerogel under a vacuum before sealing it with a capping layer. The compressive modulus can be increased sixfold by CVD treatments of the silica aerogel, such as with hexachlorodisilane as described in K. A. D. Obrey, et al., "Enhancing mechanical properties of silica aerogels," Journal of Non-Crystalline Solids, 357 (2011) 3435-3441 [Obrey] incorporated herein by reference, without significantly affecting the aerogel porosity and surface area; hence, the thermal conductivity. Additionally, CVD treatment may provide a silica aerogel that has no water absorption and a good dielectric constant (about 2.0). Silica aerogels may attain even lower thermal conductivities, such as 5-10 mW/m-K, by being pyrolized at 500° C. for 1 hour to create porosity above 90%, but may then become structurally weaker.

TIL **140** may include alumina aerogels, such as, for example, as described by J. F. Poco, et al., "Synthesis of high porosity, monolithic alumina aerogels", Journal of Non-Crystalline Solids, 285 (2001) 57-63 [Poco] incorporated herein by reference. Poco sol-gel synthesized strong (elastic modulus of 550 kPa) and low density (37 kg/m<sup>3</sup>) alumina aerogels

that showed thermal conductivities of 29, 98, and 298 mW/m-K at  $30^{\circ}$  C.,  $400^{\circ}$  C. and  $800^{\circ}$  C. respectively. The alumina aerogels formed did not sinter or appreciably shrink until exposed to temperatures above  $950^{\circ}$  C. Opacification and CVD hardening may also be utilized for alumina aerogels.

Additionally, phosphate aerogels, such as, for example, AlPO<sub>4</sub> as described in D. A. Lindquist, et al., "Boron Phosphate and Aluminum Phosphate Aerogels", Proceedings Arkansas Academy of Sciences, vol. 48, pp. 100-103 (1994) [Lindquist] incorporated herein by reference, and showed stability of surface area and pore radius to 800° C., may be utilized

TIL 140 may include carbon aerogels, such as, for example, as described by M. Wiener, et al., "Carbon Aerogel- 15 Based High Temperature Thermal Insulation" International Journal of Thermophysics (2009) 30:1372-1385 [Weiner] incorporated herein by reference. Wiener generated monolithic carbon aerogels via pyrolysis of porous organic precursors synthesized with the sol-gel method. These carbon aero- 20 gels were stable up to the two pyrolysis temperatures (800 & 1800° C.) and had thermal conductivities of 90 mW/m-K in vacuum and 120 mW/m-K in 0.1 MPa Ar atmosphere at 1500° C. A carbon aerogel pyrolized at 800° C. had a thermal conductivity of 20 mW/m-K at 300° C. in vacuum, and would 25 be expected about double at 800° C. carbon aerogels, however, need to be protected from exposure to oxygen and oxidizing environments and can have electrically conductive forms. A carbon aerogel containing TIL 140 layer may have sub-layers to minimize the diffusion to or exposure of the 30 carbon aerogel to oxygen and oxidizing environments, for example, surrounding the carbon aerogel above and below with thin sub-layers of an oxygen diffusion resistant material, for example, silicon nitride. The carbon aerogel protective sub-layers, for example, silicon nitride, could have a thick- 35 ness of greater than about 5 nm, greater than about 10 nm, greater than about 50 nm, or greater than about 100 nm. A conductive carbon aerogel layer may be utilized as an emf shield between the two layers of transistors and devices or other electrical function, such as a back-bias for the transis- 40 tors and devices formed in layer being processed 160.

TIL **140** may include nanoscale layered oxides, such as, for example, as described by J. Alvarez-Quintana, et al., "Ultra-Low Thermal Conductivity in Nanoscale Layered Oxides", Journal of Heat Transfer, vol. 132, pp. 032402-1 to 032402-6 (March 2010) [Alvarez-Quintana] incorporated herein by reference. Alvarez-Quintana showed various nanostructured layered materials of high thermal stability such as SiO<sub>2</sub>/Y<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>/Cr<sub>2</sub>O<sub>3</sub>, and SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>, and obtained a thermal conductivity of 160 mW/m-K at 27° C. for a single 10 nm/10 50 nm bilayer of the Yittria (SiO<sub>2</sub> alone about 1,400 mW/m-K). The nanoscale layered oxides showed good thermal stability up to 1100° C. and were prepared by e-beam PVD, yet may also be prepared with plasma spray to obtain lower thermal conductivities.

TIL **140** may include disordered nanostructured materials, such as, for example, as described by C. Chiritescu, "Ultra Low Thermal Conductivity in Layered Disordered Crystalline Materials," Ph.D. dissertation, U. of Illinois at Urbana-Champaign, 2010 [Chiritescu] incorporated herein by reference. Chiritescu formed thin films of disordered layered crystalline materials, for example, WSe<sub>2</sub> of 30 nm-480 nm thickness, which exhibited 50 mW/m-K thermal conductivity at room temperature. The elemental components are thermally evaporated in a high vacuum chamber to form an amorphous alloy and then heat treated at about 625° C. for about an hour to form the crystallized structure.

16

TIL 140 may include low k porous dielectric materials such as porous silsesquioxanes, such as, phenyl, vinyl, and Methylsilsesquioxane (MSQ), and silsesquioxane blends of them, and other porous Xerogel films, for example, as described by N. Ahner, et al., "Thermal stability and gap-fill properties of spin-on MSQ low k dielectrics," Microelectronic Engineering, 84 (32007) 2606-2609 [Ahner] and C. Hu., et al., "Thermal conductivity study of porous low-k dielectric materials," Applied Physics Letters, vol. 77, issue 1, July 2000 [Hu], both incorporated herein by reference. Hu found that at Xerogel porosities of greater than 70% the thermal conductivity is about 100 mW/m-K Ahner found good porosities with the commercial Rohm and Haas Zirkon LK2000, and Honeywell ACCUGLASSTM T-512B spin on products, but their physical and electrical properties were only stable to about 650° C.

TIL 140 may include a top sub-layer of a material whose thermal conductivity decreases with temperature, for example, germanium, and a lower sub-layer with a material whose thermal conductivity increases with temperature, for example, silica aerogels. For example, at about  $800^{\circ}$  C., the thermal conductivity of germanium is about 150 mW/m-K, whereas at about room temperature the germanium thermal conductivity is about 580 mW/m-K.

TIL 140 may include thick silicon oxides, for example greater than about 5 um or greater than about 10 um in thickness or greater than about 30 um in thickness. TIL 140 may include silicon oxide sub-layer or layers combined with IR absorbing sub-layers, for example,  ${\rm TiO_2}$  or carbon, for example about 50 nm, about 100 nm, about 200 nm thick, about 500 nm thick each. The IR absorbing sub-layer or layers may be placed closer to the layer being processed 160 than most of the oxide sub-layers.

TIL 140 may include more than one aerogel layer, and the sub-layer on top may have different thermal and optical characteristics than the one below. For example, as illustrated in FIG. 1B, a higher temperature stable TIL material 144 may be placed on top of a lower temperature stable TIL material 142. For example, higher temperature stable TIL material 144 may also have a greater thermal conductivity and/or IR absorbing properties than lower temperature stable TIL material 142. For example, higher temperature stable TIL material 144 may include a carbon or alumina aerogel and lower temperature stable TIL material 142 may include, for example, a silica aerogel or a disordered nanostructured material such as WSe<sub>2</sub>, when the two TIL sub-layers are utilized in combination. Moreover, two thin layers of a crack sensitive material, for example, some aerogels, may be formed (with or without an oxide layer disposed in-between) in sequence or separately, and combined as a portion of or substantially all of TIL 140. Choice of material and structure may include the maximum temperature during processing of layer being processed 160.

TIL 140 may include at least one layer or region of highly thermally conductive material, for example, such as graphene, to improve the horizontal heat conductivity and thermal uniformity of the TIL 140 and/or the TPS.

TIL 140 may include structures which include the purpose of enhancing the physical strength and/or cracking resistance of the TIL. For example, as illustrated in FIG. 1C, strengthening regions 134 may be placed within TIL 140 to stiffen and/or mechanically strengthen the 3DIC structure. Strengthening regions 134 may provide smaller regions of material, such as aerogel, to cure and may mitigate cracking and fracture initiation and/or propagation. Strengthening regions 134 may include materials that have a higher Young's modulus than the majority of the material within TIL 140. Strengthening regions 134 may include, for example, silicon oxide,

which has a higher mechanical strength than, for example, most aerogels and silsesquioxanes. Strengthening regions **134** may include less than about 0.5%, less than about 1%, less than about 2%, or less than about 3% of the area and/or volume of TIL 140, thus affecting the total average TIL 140 5 thermal conductivity by less than about 1%, or less than about 3%. Strengthening regions 134 may be constructed to substantially match the thickness of TIL 140, or may be about 80%, or about 60% or about 50% or about 30% of the thickness of TIL 140. To help mitigate the increased local thermal conductivity due to the presence of strengthening regions 134, the strengthening regions 134 may be designed to not overlap (or may partially overlap, not shown) another strengthening regions 134 above or below, as illustrated in FIG. 1D. Moreover, as illustrated in FIG. 1E, strengthening 15 regions 134 may be designed to be aligned to the scribelanes, for example scribelane with thermal via stacks and continuous shield 120 and/or scribelane with thermal via stacks and cut shield layer 122, and may underlap the full extent of the scribelanes by underlap 135, which may be the layout dis- 20 tance between the die seal 106 and the edge of the closest strengthening regions 134. The value of underlap 135 may be determined at least by the materials and structure of upper isolation layer 132, strengthening regions 134, or lower isolation layer 130, and shield layer or regions 118 (thermal 25 conductivities and thicknesses), the maximum desired temperature of 160, damage/melting point of temperature sensitive substrate metallization 108 and/or BEOL isolation 110 and/or die seal 106. For example, underlap 135 may have the dimension of at least about 1 um, at least about 5 um, at least 30 about 10 um, at least about 20 um, or at least about 50 um.

Continuing as illustrated in FIG. 1A (and in a similar fashion for FIGS. 1B-1E), upper isolation layer 132 may be deposited on top of TIL 140 to seal, protect, and electrically (and a small bit thermally) isolate, and may include the bond- 35 ing oxides for an ion-cut layer transfer process (for example, the case wherein TIL 140 is formed on the acceptor wafer). A shield layer (not shown) may be placed above the TIL 140 as needed to thermally protect the TIL from pulsed short timescale laser exposures, which may be utilized in combination 40 with conventional (with cooled chuck) thermal processing steps. The heat capacity of the shield layer is more than sufficient to absorb the energy dissipated by the layer being processed 160 as it cools; the heat capacity in the shield may be designed to absorb and dissipate the energy, such as 45 described in referenced documents herein and by Rajendran, B., et al., "Pulsed Laser Annealing: A scalable and practical technology for monolithic 3D IC," IEEE 3DIC Symposium, October 2013, [Rajendran2013] incorporated herein by reference. Upper isolation layer 132 may include designed-in 50 voids (not shown), for example, by etch removal of portions of upper isolation layer 132, thus forming regions of vacuum and/or gas and regions of the remaining material (for example, silicon oxide) of upper isolation layer 132. The voids may be formed such that they extend fully or partially 55 thru the entire thickness upper isolation layer 132. The presence of the voids may reduce the average thermal conductivity of upper isolation layer 132. The voids may include greater than about 5%, greater than about 10%, greater than about 20%, or greater than about 40% of the area and/or volume of 60 upper isolation layer 132, thus affecting the total average upper isolation layer 132 thermal conductivity by greater than about 5%, or greater than about 40%.

The layer being processed **160** may include a layer transferred thin (less than 200 nm) layer that may be oxide to oxide 65 bonded to the top surface of the built-up substrate (for example, a portion of upper isolation layer **132**), thereby

18

including a bonding oxide that partially thermally and fully electrically isolates the layer being processed from the (top) shield layer. The layer being processed 160 may include materials such as, for example, monocrystalline silicon, or InP, or GaAs, or Ge, or SiGe, or SiC, or combinations thereof. The layer being processed 160 may also include a heat spreader and/or optical reflective layer or layers, for example tungsten or aluminum, and/or may include optically absorptive layers or regions, for example carbon, phase change materials. The layer being processed 160 may also be formed by methods other than layer transfer, for example, by deposition, and may include poly-crystalline silicon, amorphous silicon, carbon nano-tubes, grapheme, MoS<sub>2</sub>. During the formation of devices, for example transistors, diodes, optical devices, resistors, inductors, as well as other devices described herein and in referenced documents, on the layer being processed 160, the structures and methods described herein, for example, the TPS, TIL, TES, and modified processing equipment, may protect the underlying sensitive structures from the processing and processing temperature exposures of that device formation. The layer being processed 160 may include the second or higher transferred or constructed device layers in the 3DIC devices and methods disclosed in the referenced documents, for example, transfer layer 809 of FIG. 8C of U.S. Pat. No. 8,273,610.

The goal is to engineer heat transfer in this stack, such that the temperature in substrate metallization **108** and BEOL isolation **110** interconnect layers and substrate device regions **102** are kept cool, below preferably about 200° C., or below about 350° C., or below about 400° C., depending on the precise thermal sensitivities of the BEOL materials and construction. There are two regimes of interest, which must be considered from the standpoint of heat transfer.

For short-duration, high-temperature process steps, the goal is to engineer the heat capacity in the shield layer(s), for example, shield layer or regions 118, to be large enough to serve as a 'sink' for the thermal energy involved in such process steps. The thermal energy which must be dissipated is, for instance, the energy to melt/sub-melt the thin Si layer (in order to anneal damage from ion implantation and electrically activate the dopants). This thermal energy, per unit area, is given in the first equation, below. The second equation represents the storage of this energy in the shield layer.

$E_{\textit{dissipated}} / A = \rho_{Si} t_{Si} C_{Si} \Delta T_{Si}$

$E_{stored}/A = \rho_{shield}t_{shield}C_{shield}\Delta T_{shield}$

In order that underlying structures are affected minimally, the temperature change in the shield layer or regions 118 should be less than about 200° C. or less than about 400° C., compared to a temperature rise in the surface Si layer of about 1400° C. Such a condition is arranged by ensuring the product of the Si layer thickness and heat capacity per unit volume are roughly 1/4 of the similar parameters for the shield layer. The shield layer then dissipates this energy slowly enough into the underlying structures, such that the underlying structures temperature should not rise above about 200° C. or less than about 400° C. The TPS, which may include shield layer or regions 118 may allow for rapid and uniform lateral heat spreading of heat coming from above, avoidance of hot-spots, and to provide good thermal connectivity (thru, for example, thermal via stacks with via landing pads 112 and/or thermal vias in the scribelane 114, and/or in-die thermal via stacks 116 and/or fill-in thermal paths 117, and/or die seal 106) to the cooled substrate 100 for further protection of the underlying circuits substrate device regions 102 and substrate metallization 108 and BEOL isolation 110 interconnect layers.

For long-duration, low-to-mid-temperature process steps, for example, above about 405° C. to about 1000° C., the goal changes. Underlying structures must not be damaged or changed. But, there is too much thermal energy to simply store it in a shield layer: the layer would have to be far too 5 massive. Instead, the layer-to-layer thermal conductivities must be engineered, so that the heat flux through the surface and thin Si layer (layer being processed 160) is sufficient to achieve the process goals, but the same heat flux in underlying layers causes only a temperature rise of perhaps about 200° C. This different goal may be achieved through two means: having a thermal insulation layer (for example TIL 140) above the shield layer (for example shield layer or regions 118) which has a very low thermal conductivity; and/or, placing the entire stack of materials, wafer and all, on a chuck or 15 substrate whose temperature is held actively at a low value, for example, at roughly room temperature.

Persons of ordinary skill in the art will appreciate that the illustrations in FIGS. 1A through 1E are exemplary only and are not drawn to scale. Such skilled persons will further 20 appreciate that many variations are possible such as, for example, substrate 100 may be p-type, n-type or un-doped silicon, or may be a structured material wafer such as GeOI, a mix of Si and Ge, SiGe. Moreover, MOSFETs may be constructed with n-MOSFETs in a first mono-crystalline sili- 25 con layer such as substrate 100 and p-MOSFETs in a second mono-crystalline layer, such as layer to be processed 160, which may include different crystalline orientations of the mono-crystalline silicon layers, such as for example, <100>, <111> or <551>. Many other modifications within the scope 30 of the invention will suggest themselves to such skilled persons after reading this specification. Thus the invention is to be limited only by the appended claims.

As illustrated in FIG. 2, the structure and device of FIG. 1 may be modeled as a series of thermal resistors (with units of 35 K/W, degrees Kelvin per Watt) between layer being processed 160 being heated by a heat source and a cooled chuck 291. TIL stack 292, which may include upper isolation layer 132, TIL 140, and lower isolation layer 130, may be disposed between the layer being processed 160 and heat shield layer 40 or region 118. Base circuits 293, which may include substrate device regions 102 (or a portion), die seal 106, regions of substrate metallization 108 and BEOL isolation 110, thermal via stacks with via landing pads 112, thermal vias in the scribelane 114, in-die thermal via stacks 116, fill-in thermal 45 paths 117, and via connection 119, may be disposed between heat shield layer or region 118 and substrate 100. Substrate 100 may be in contact with cooled chuck 291 at backside surface 104.

For example, suppose a heat source heats the layer being 50 processed **160** to 1000° C. and the cooled chuck **291** is being held at 20° C. by means of, for example, cooling fluids or gases. For simplicity the horizontal patterning in the base circuit will be ignored. The following equations and calculations follow

$Rx \propto Tx^*/\kappa$ ; where Rx is the average thermal resistance of the layer x, Tx is the thickness of the layer x, and  $\kappa$  is the average thermal conductivity of the layer x.

$R_{UT} \propto T_{UT}/0.1=10T_{UT}$ ; where  $R_{UT}$  is the average thermal resistance of TIL stack **292**,  $T_{UT}$  is the thickness of TIL stack 60 **292**, and the thermal conductivity of TIL stack **292** is about 0.1 W/m-K, ignoring the small effect of upper isolation layer **132** and lower isolation layer **130**.

$R_{BC} \propto 2/(400*0.5+1.4*0.5)+2/(400*0.05+1.4*0.95)=$  0.104; where  $R_{BC}$  is the average thermal resistance of base 65 circuits 293, the base circuits 293 layer is 4 um thick, the metal layer volume mix is 50% SiO<sub>2</sub>@  $\kappa$ =1.4 W/m-K and

20

50% Cu @  $\kappa$  =400 W/m-K, and the IMD intra-layer volume mix is 95% SiO  $_2$  with 5% Cu vias.

$R_{SS} \propto 775/150=5.2$ ; where  $R_{SS}$  is the average thermal resistance of substrate 100, and substrate 100 is a 300 mm bulk silicon substrate of 775 um thickness and  $\kappa \approx 150$  W/m-K.

Assuming the chuck to be close to  $0^{\circ}$  C. and a  $1000^{\circ}$  C. processing temperature of layer being processed **160**, gives, for the elements and structure and devices within base circuits **293** not to exceed  $400^{\circ}$  C.:  $400/1000 \ge 5.3/(10T_{UI} + 5.3)$ . Solving for  $T_{UI}$  gives  $T_{UI} \ge 0.8$  um.

Accordingly, base circuits **293** of temperatures below 400° C. may be achieved with a TIL stack **292** layer thickness of about 1 um. Further, the result is insensitive to the actual thickness of the base circuits **293** because the substrate **100** thickness term dominates. Finally, the few phonon reflections of the base circuits **293** BEOL structures do not appreciably affect the  $R_{BC}$ , which is a non-dominant term as well.

However, a 1 um TIL stack of 0.1 W/m-K thermal conductivity for a 400° C. temperature drop across it computes to about a 5.4 MW cooler capacity requirement for a 300 mm silicon wafer. This may be not be readily achievable as Tuckermann demonstrated that a water based substrate cooling capacity may be about 1 kW/cm<sup>2</sup>, which on a 300 mm silicon wafer/substrate may be about 700 kW/wafer (Tuckerman, D. B., et al., "High Performance Heat Sinking for VLSI," IEEE Electron Device Letters, vol. ed1-2, no. 5, May 1981. The DARPA based ICECool program has achieved higher thermal cooling results. In addition, the cooling capacity of equipment chuck coolers may limit the amount of heat that can be removed from the chuck to about 100 kW/300 mm wafer, and practical/economical equipment heater and cooler designs may further limit the amount of heat that can be removed from the chuck to about 10 kW/300 mm wafer. A thicker TIL may be desirable to create a high enough thermal resistance so that the layer being processed 160 may be at the desired processing temperature of 600/800/1000° C., and the cooling capacity limitations may be kept. A TIL stack thickness of about 10 um may be enough whilst the thermal processing on layer being processed 160 is being performed. This TIL thickness may be adjusted by considerations of TIL thermal conductivity, desired temperature of the layer being processed, and equipment capacity/capability constraints.

TPS protective device structure shown in at least FIGS. 1 and 2 herein may assist guiding the heat from the layer being processing 160 safely to the cooling chuck or cooling device. Heat from a processing step of forming devices and structure in and on the layer being processed 160 may flow through the TIL stack 292 to the one or more shield layers such as shield layer or regions 118, where the heat may preferentially flow in the very thermally conductive shield layer horizontally until finding a vertical path of high thermal conductivity, for example, the scribelane or in-die thermal via stacks. The heat may then be conducted thru the substrate 100 to the back surface 104 of the substrate 100 which is coupled to a cooling chuck or other cooling device that draws the processing heat away. Shield layers, such as shield layer or regions 118, and thermal vias and via stacks, including thermal via stacks with via landing pads 112, thermal vias in the scribelane 114, in-die thermal via stacks 116, may include materials with a high thermal conductivity greater than 10 W/m-K, for example, copper (about 400 W/m-K), aluminum (about 237 W/m-K), Tungsten (about 173 W/m-K), Plasma Enhanced Chemical Vapor Deposited Diamond Like Carbon-PECVD DLC (about 1000 W/m-K), and Chemical Vapor Deposited (CVD) graphene (about 5000 W/m-K). Shield layers, such as shield layer or regions 118, and thermal vias and via stacks, including thermal via stacks with via landing pads 112, ther-